Cray-1 - Cray-1

| Cray-1 | |

|---|---|

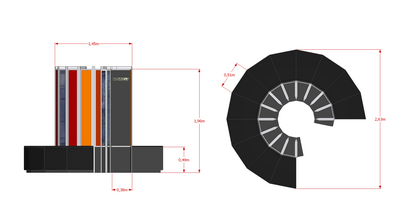

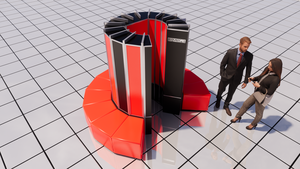

Representación 3D de dos Cray-1 con una figura como escala

| |

| Diseño | |

| Fabricante | Investigación de Cray |

| Diseñador | Seymour Cray |

| Fecha de lanzamiento | 1975 |

| Unidades vendidas | Más de 80 |

| Precio | US $ 7,9 millones en 1977 (equivalente a $ 33,7 millones en 2020) |

| Caja | |

| Dimensiones | Altura: 196 cm (77 pulgadas ) de diámetro. (base): 263 cm (104 pulgadas ) de diámetro. (columnas): 145 cm (57 pulgadas) |

| Peso | 5,5 toneladas (Cray-1A) |

| Poder | 115 kW a 208 V 400 Hz |

| Sistema | |

| Interfaz | Eclipse general de datos |

| Sistema operativo | COS Y UNICOS |

| UPC | Procesador de 64 bits a 80 MHz |

| Memoria | 8,39 megabytes (hasta 1048576 palabras) |

| Almacenamiento | 303 Megabytes (Unidad DD19) |

| FLOPS | 160 MFLOPS |

| Sucesor | Cray X-MP |

El Cray-1 fue un superordenador diseñado, fabricado y comercializado por Cray Research . Anunciado en 1975, el primer sistema Cray-1 se instaló en el Laboratorio Nacional de Los Alamos en 1976. Con el tiempo, se vendieron más de 100 Cray-1, convirtiéndolo en una de las supercomputadoras más exitosas de la historia. Quizás sea más conocido por su forma única, un gabinete en forma de C relativamente pequeño con un anillo de bancos alrededor del exterior que cubre las fuentes de alimentación y el sistema de enfriamiento.

El Cray-1 fue el primer superordenador en implementar con éxito el diseño del procesador vectorial . Estos sistemas mejoran el rendimiento de las operaciones matemáticas al organizar la memoria y los registros para realizar rápidamente una sola operación en un gran conjunto de datos. Los sistemas anteriores como CDC STAR-100 y ASC habían implementado estos conceptos, pero lo hicieron de una manera que limitaba seriamente su desempeño. El Cray-1 abordó estos problemas y produjo una máquina que funcionaba varias veces más rápido que cualquier diseño similar.

El arquitecto del Cray-1 fue Seymour Cray ; el ingeniero jefe fue el cofundador de Cray Research, Lester Davis. Continuarían diseñando varias máquinas nuevas utilizando los mismos conceptos básicos y conservaron la corona de rendimiento en la década de 1990.

Historia

De 1968 a 1972, Seymour Cray de Control Data Corporation (CDC) trabajó en el CDC 8600 , el sucesor de sus diseños anteriores CDC 6600 y CDC 7600 . El 8600 se componía esencialmente de cuatro 7600 en una caja con un modo especial adicional que les permitía operar con paso de bloqueo de una manera SIMD .

Jim Thornton, anteriormente socio de ingeniería de Cray en diseños anteriores, había iniciado un proyecto más radical conocido como CDC STAR-100 . A diferencia del enfoque de rendimiento de fuerza bruta del 8600, el STAR tomó una ruta completamente diferente. El procesador principal del STAR tenía un rendimiento más bajo que el del 7600, pero agregó hardware e instrucciones para acelerar las tareas de supercomputadoras particularmente comunes.

En 1972, el 8600 había llegado a un callejón sin salida; la máquina era tan increíblemente compleja que era imposible hacer que una funcionara correctamente. Incluso un solo componente defectuoso haría que la máquina no estuviera operativa. Cray se dirigió a William Norris , director ejecutivo de Control Data, y le dijo que se necesitaba un rediseño desde cero. En ese momento, la compañía estaba en serios problemas financieros, y con STAR también en proceso, Norris no pudo invertir el dinero.

Como resultado, Cray dejó los CDC y comenzó Cray Research muy cerca del laboratorio de los CDC. En el patio trasero del terreno que compró en Chippewa Falls , Cray y un grupo de ex empleados de los CDC comenzaron a buscar ideas. Al principio, el concepto de construir otra supercomputadora parecía imposible, pero después de que el Director de Tecnología de Cray Research viajó a Wall Street y encontró una alineación de inversores dispuestos a respaldar a Cray, todo lo que se necesitaba era un diseño.

Durante cuatro años, Cray Research diseñó su primera computadora. En 1975 se anunció el Cray-1 de 80 MHz. La emoción fue tan alta que estalló una guerra de ofertas por la primera máquina entre el Laboratorio Nacional Lawrence Livermore y el Laboratorio Nacional de Los Alamos , este último finalmente ganó y recibió el número de serie 001 en 1976 para una prueba de seis meses. El Centro Nacional de Investigaciones Atmosféricas (NCAR) fue el primer cliente oficial de Cray Research en 1977, pagando 8,86 millones de dólares (7,9 millones de dólares más 1 millón de dólares por los discos) por el número de serie 3. La máquina NCAR se desmanteló en 1989. La empresa esperaba para vender quizás una docena de las máquinas y establecer el precio de venta en consecuencia, pero finalmente se vendieron más de 80 Cray-1 de todos los tipos, a un precio de $ 5 millones a $ 8 millones. La máquina convirtió a Seymour Cray en una celebridad y a su empresa en un éxito, que duró hasta el colapso de la supercomputadora a principios de la década de 1990.

Basado en una recomendación del estudio de William Perry , la NSA compró un Cray-1 para la investigación teórica en criptoanálisis . Según Budiansky, "Aunque las historias estándar de Cray Research persistirían durante décadas al afirmar que el primer cliente de la empresa fue el Laboratorio Nacional de Los Alamos, de hecho era la NSA ..."

El 160 MFLOPS Cray-1 fue reemplazado en 1982 por el 800 MFLOPS Cray X-MP , el primer ordenador multiprocesador Cray. En 1985, el muy avanzado Cray-2 , capaz de un rendimiento máximo de 1.9 GFLOPS, sucedió a los dos primeros modelos, pero tuvo un éxito comercial algo limitado debido a ciertos problemas para producir un rendimiento sostenido en aplicaciones del mundo real. Por lo tanto, se hizo un sucesor evolutivo de diseño más conservador de los modelos Cray-1 y X-MP con el nombre de Cray Y-MP y se lanzó en 1988.

En comparación, el procesador en un dispositivo inteligente típico de 2013, como un Google Nexus 10 o HTC One , funciona a aproximadamente 1 GFLOPS, mientras que el procesador A13 en un iPhone 11 de 2020 funciona a 154,9 GFLOPS, una marca de supercomputadoras que sucede al Cray-1. no llegaría hasta 1994 .

Fondo

Las cargas de trabajo científicas típicas consisten en leer grandes conjuntos de datos, transformarlos de alguna manera y luego volver a escribirlos. Normalmente, las transformaciones que se aplican son idénticas en todos los puntos de datos del conjunto. Por ejemplo, el programa puede sumar 5 a cada número en un conjunto de un millón de números.

En las computadoras tradicionales, el programa recorre todos los millones de números, sumando cinco, ejecutando así un millón de instrucciones que dicen a = add b, c. Internamente, la computadora resuelve esta instrucción en varios pasos. Primero lee la instrucción de la memoria y la decodifica, luego recopila cualquier información adicional que necesite, en este caso los números byc, y finalmente ejecuta la operación y almacena los resultados. El resultado final es que la computadora requiere decenas o cientos de millones de ciclos para realizar estas operaciones.

Máquinas vectoriales

En STAR, las nuevas instrucciones esencialmente escribieron los bucles para el usuario. El usuario le dijo a la máquina en qué lugar de la memoria se almacenaba la lista de números y luego introdujo una sola instrucción a(1..1000000) = addv b(1..1000000), c(1..1000000). A primera vista, parece que los ahorros son limitados; en este caso, la máquina busca y descodifica sólo una única instrucción en lugar de 1.000.000, lo que ahorra 1.000.000 de búsquedas y descodificaciones, quizás una cuarta parte del tiempo total.

Los ahorros reales no son tan obvios. Internamente, la CPU de la computadora se construye a partir de una serie de partes separadas dedicadas a una sola tarea, por ejemplo, agregar un número o buscar en la memoria. Normalmente, a medida que la instrucción fluye a través de la máquina, solo una parte está activa en un momento dado. Esto significa que cada paso secuencial de todo el proceso debe completarse antes de que se pueda guardar un resultado. La adición de una canalización de instrucciones cambia esto. En tales máquinas, la CPU "mirará hacia adelante" y comenzará a buscar las instrucciones siguientes mientras la instrucción actual aún se está procesando. En esta línea de ensamblaje , cualquier instrucción aún requiere tanto tiempo para completarse, pero tan pronto como termina de ejecutarse, la siguiente instrucción está justo detrás de ella, con la mayoría de los pasos necesarios para su ejecución ya completados.

Los procesadores vectoriales utilizan esta técnica con un truco adicional. Debido a que el diseño de los datos está en un formato conocido, un conjunto de números ordenados secuencialmente en la memoria, las canalizaciones se pueden ajustar para mejorar el rendimiento de las recuperaciones. Al recibir una instrucción vectorial, un hardware especial configura el acceso a la memoria para las matrices y coloca los datos en el procesador lo más rápido posible.

El enfoque de los CDC en STAR utilizó lo que hoy se conoce como arquitectura de memoria-memoria . Esto se refería a la forma en que la máquina recopilaba datos. Configuró su canalización para leer y escribir en la memoria directamente. Esto permitió que STAR usara vectores de cualquier longitud, lo que lo hacía altamente flexible. Desafortunadamente, la tubería tuvo que ser muy larga para permitirle tener suficientes instrucciones en vuelo para compensar la memoria lenta. Eso significaba que la máquina incurría en un alto costo al cambiar de vectores de procesamiento a realizar operaciones en operandos individuales ubicados aleatoriamente. Además, el bajo rendimiento escalar de la máquina significaba que después de que se había producido el cambio y la máquina estaba ejecutando instrucciones escalares, el rendimiento era bastante pobre. El resultado fue un rendimiento bastante decepcionante en el mundo real, algo que quizás podría haber sido previsto por la ley de Amdahl .

El enfoque de Cray

Cray estudió el fracaso del STAR y aprendió de él. Decidió que, además del procesamiento rápido de vectores, su diseño también requeriría un excelente rendimiento escalar completo. De esa forma, cuando la máquina cambiara de modo, seguiría proporcionando un rendimiento superior. Además, observó que las cargas de trabajo podrían mejorarse drásticamente en la mayoría de los casos mediante el uso de registros .

Así como las máquinas anteriores habían ignorado el hecho de que la mayoría de las operaciones se estaban aplicando a muchos puntos de datos, STAR ignoró el hecho de que esos mismos puntos de datos serían operados repetidamente. Mientras que STAR leería y procesaría la misma memoria cinco veces para aplicar cinco operaciones vectoriales en un conjunto de datos, sería mucho más rápido leer los datos en los registros de la CPU una vez y luego aplicar las cinco operaciones. Sin embargo, hubo limitaciones con este enfoque. Los registros eran significativamente más costosos en términos de circuitos, por lo que solo se pudo proporcionar un número limitado. Esto implicaba que el diseño de Cray tendría menos flexibilidad en términos de tamaños de vector. En lugar de leer un vector de cualquier tamaño varias veces como en el STAR, el Cray-1 tendría que leer solo una parte del vector a la vez, pero luego podría ejecutar varias operaciones en esos datos antes de escribir los resultados en la memoria. Dadas las cargas de trabajo típicas, Cray consideró que el pequeño costo incurrido por tener que dividir grandes accesos secuenciales a la memoria en segmentos era un costo que bien valía la pena pagar.

Dado que la operación vectorial típica implicaría cargar un pequeño conjunto de datos en los registros vectoriales y luego ejecutar varias operaciones en él, el sistema vectorial del nuevo diseño tenía su propia tubería separada. Por ejemplo, las unidades de multiplicación y suma se implementaron como hardware separado, por lo que los resultados de una se podrían canalizar internamente al siguiente, ya que la decodificación de instrucciones ya se había manejado en la canalización principal de la máquina. Cray se refirió a este concepto como encadenamiento , ya que permitía a los programadores "encadenar" varias instrucciones y obtener un mayor rendimiento.

Descripción

La nueva máquina fue el primer diseño de Cray en utilizar circuitos integrados (CI). Aunque los circuitos integrados habían estado disponibles desde la década de 1960, solo a principios de la década de 1970 alcanzaron el rendimiento necesario para aplicaciones de alta velocidad. El Cray-1 usó solo cuatro tipos de IC diferentes, una puerta ECL dual 5-4 NOR (una de 5 entradas y una de 4 entradas, cada una con salida diferencial), otra puerta MECL 10K 5-4 NOR más lenta utilizada para la distribución de direcciones , una RAM estática (SRAM) de 16 × 4 bits de alta velocidad (6 ns) utilizada para los registros y una SRAM de 1.024 × 1 bit y 48 ns utilizada para la memoria principal. Estos circuitos integrados fueron suministrados por Fairchild Semiconductor y Motorola . En total, el Cray-1 contenía unas 200.000 puertas.

Los circuitos integrados se montaron en grandes placas de circuito impreso de cinco capas , con hasta 144 circuitos integrados por placa. Luego se montaron los tableros espalda con espalda para enfriarlos (ver más abajo) y se colocaron en veinticuatro estantes de 28 pulgadas de alto (710 mm) que contenían 72 tableros dobles. El módulo típico (unidad de procesamiento distinta) requería una o dos placas. En total, la máquina contenía 1.662 módulos en 113 variedades.

Cada cable entre los módulos era un par trenzado , cortado a una longitud específica para garantizar que las señales llegaran en el momento preciso y minimizar la reflexión eléctrica. Cada señal producida por los circuitos ECL era un par diferencial, por lo que las señales estaban equilibradas. Esto tendía a hacer que la demanda de la fuente de alimentación fuera más constante y a reducir el ruido de conmutación. La carga de la fuente de alimentación estaba tan equilibrada que Cray se jactó de que la fuente de alimentación no estaba regulada. Para la fuente de alimentación, todo el sistema informático parecía una simple resistencia.

Los circuitos ECL de alto rendimiento generaron un calor considerable y los diseñadores de Cray dedicaron tanto esfuerzo al diseño del sistema de refrigeración como al resto del diseño mecánico. En este caso, cada placa de circuito se emparejó con una segunda, colocada espalda con espalda con una hoja de cobre entre ellas. La lámina de cobre conducía el calor a los bordes de la jaula, donde el freón líquido que corría por los tubos de acero inoxidable lo arrastraba hacia la unidad de enfriamiento debajo de la máquina. El primer Cray-1 se retrasó seis meses debido a problemas en el sistema de enfriamiento; El lubricante que normalmente se mezcla con el freón para mantener el compresor en funcionamiento podría filtrarse a través de los sellos y eventualmente cubrir las tablas con aceite hasta que se cortocircuiten. Se tuvieron que utilizar nuevas técnicas de soldadura para sellar adecuadamente la tubería.

Para sacar la máxima velocidad de la máquina, todo el chasis se dobló en una gran forma de C. Las partes del sistema que dependían de la velocidad se colocaron en el "borde interior" del chasis, donde las longitudes de los cables eran más cortas. Esto permitió que el tiempo de ciclo se redujera a 12,5 ns (80 MHz), no tan rápido como el 8600 de 8 ns al que había renunciado, pero lo suficientemente rápido como para vencer al CDC 7600 y al STAR. NCAR estimó que el rendimiento general del sistema era 4,5 veces mayor que el del CDC 7600.

El Cray-1 se construyó como un sistema de 64 bits , una desviación del 7600/6600, que eran máquinas de 60 bits (también se planeó un cambio para el 8600). El direccionamiento fue de 24 bits, con un máximo de 1.048.576 palabras de 64 bits (1 megapalabra) de memoria principal, donde cada palabra también tenía 8 bits de paridad para un total de 72 bits por palabra. Había 64 bits de datos y 8 bits de verificación. La memoria se distribuyó en 16 bancos de memoria intercalados , cada uno con un tiempo de ciclo de 50 ns, lo que permitía leer hasta cuatro palabras por ciclo. Las configuraciones más pequeñas podrían tener 0,25 o 0,5 megapalabras de memoria principal. El ancho de banda máximo de memoria agregada fue de 638 Mbit / s.

El conjunto de registros principal constaba de ocho registros escalares (S) de 64 bits y ocho registros de direcciones (A) de 24 bits. Estos estaban respaldados por un conjunto de sesenta y cuatro registros cada uno para el almacenamiento temporal S y A conocidos como T y B respectivamente, que no podían ser vistos por las unidades funcionales. El sistema vectorial agregó otros ocho registros vectoriales (V) de 64 elementos por 64 bits, así como una longitud vectorial (VL) y una máscara vectorial (VM). Finalmente, el sistema también incluía un registro de reloj en tiempo real de 64 bits y cuatro búferes de instrucciones de 64 bits que contenían sesenta y cuatro instrucciones de 16 bits cada uno. El hardware se configuró para permitir que los registros vectoriales se alimentaran con una palabra por ciclo, mientras que los registros de direcciones y escalares requerían dos ciclos. Por el contrario, todo el búfer de instrucciones de 16 palabras podría llenarse en cuatro ciclos.

El Cray-1 tenía doce unidades funcionales canalizadas. La aritmética de direcciones de 24 bits se realizó en una unidad de suma y una unidad de multiplicación. La parte escalar del sistema constaba de una unidad de suma, una unidad lógica, un recuento de población , una unidad de recuento de cero inicial y una unidad de desplazamiento. La parte del vector constaba de unidades de suma, lógica y desplazamiento. Las unidades funcionales de coma flotante se compartían entre las porciones escalar y vectorial, y estas consistían en unidades de aproximación de suma, multiplicación y recíproca.

El sistema tenía un paralelismo limitado. Podría emitir una instrucción por ciclo de reloj, para un rendimiento teórico de 80 MIPS , pero con la multiplicación y suma de puntos flotantes vectoriales en paralelo, el rendimiento teórico fue de 160 MFLOPS. (La unidad de aproximación recíproca también podría operar en paralelo, pero no arrojó un resultado de punto flotante verdadero; se necesitaban dos multiplicaciones adicionales para lograr una división completa).

Puesto que la máquina fue diseñada para operar con grandes conjuntos de datos, el diseño también dedica un considerable circuitos de E / S . Los diseños anteriores de Cray en CDC habían incluido computadoras separadas dedicadas a esta tarea, pero esto ya no era necesario. En cambio, el Cray-1 incluía cuatro controladores de 6 canales, cada uno de los cuales tenía acceso a la memoria principal una vez cada cuatro ciclos. Los canales tenían 16 bits de ancho e incluían 3 bits de control y 4 para la corrección de errores, por lo que la velocidad de transferencia máxima era de 1 palabra por 100 ns, o 500 mil palabras por segundo para toda la máquina.

El modelo inicial, el Cray-1A , pesaba 5,5 toneladas, incluido el sistema de refrigeración Freon. Configurada con 1 millón de palabras de memoria principal, la máquina y sus fuentes de alimentación consumieron alrededor de 115 kW de potencia; el enfriamiento y el almacenamiento probablemente más que duplicaron esta cifra. Una minicomputadora Data General SuperNova S / 200 sirvió como unidad de control de mantenimiento (MCU), que se usó para alimentar el sistema operativo Cray en el sistema en el momento del arranque, para monitorear la CPU durante el uso y, opcionalmente, como computadora frontal. La mayoría, si no todos, los Cray-1A se entregaron utilizando el siguiente Data General Eclipse como MCU.

Cray-1S

El Cray-1S , anunciado en 1979, era un Cray-1 mejorado que admitía una memoria principal más grande de 1, 2 o 4 millones de palabras. La memoria principal más grande fue posible gracias al uso de circuitos integrados de RAM bipolares de 4.096 x 1 bit con un tiempo de acceso de 25 ns. Las minicomputadoras de Data General se reemplazaron opcionalmente por un diseño interno de 16 bits que se ejecuta a 80 MIPS. El subsistema de E / S se separó de la máquina principal, se conectó al sistema principal a través de un canal de control de 6 Mbit / sy un canal de datos de alta velocidad de 100 Mbit / s. Esta separación hizo que el 1S pareciera dos "medios Crays" separados por unos pocos pies, lo que permitió que el sistema de E / S se expandiera según fuera necesario. Los sistemas se pueden comprar en una variedad de configuraciones desde el S / 500 sin E / S y 0,5 millones de palabras de memoria hasta el S / 4400 con cuatro procesadores de E / S y 4 millones de palabras de memoria.

Cray-1M

El Cray-1M , anunciado en 1982, reemplazó al Cray-1S. Tenía un tiempo de ciclo de 12 ns más rápido y usaba una RAM MOS menos costosa en la memoria principal. El 1M se suministró en sólo tres versiones, el M / 1200 con 1 millón de palabras en 8 bancos, o el M / 2200 y M / 4200 con 2 o 4 millones de palabras en 16 bancos. Todas estas máquinas incluían dos, tres o cuatro procesadores de E / S, y el sistema agregó un segundo canal de datos de alta velocidad opcional. Los usuarios pueden agregar un dispositivo de almacenamiento de estado sólido con 8 a 32 millones de palabras de RAM MOS.

Software

En 1978 se lanzó el primer paquete de software estándar para Cray-1, que consta de tres productos principales:

- Sistema operativo Cray (COS) (las máquinas posteriores ejecutarían UNICOS , la versión UNIX de Cray )

- Lenguaje ensamblador Cray (CAL)

- Cray FORTRAN (CFT), el primer compilador de Fortran que vectoriza automáticamente

Los sitios financiados por el Departamento de Energía de los Estados Unidos del Laboratorio Nacional Lawrence Livermore , el Laboratorio Científico de Los Alamos , los Laboratorios Nacionales Sandia y los centros de supercomputadoras de la Fundación Nacional de Ciencias (para la física de alta energía) representaron el segundo bloque más grande con el Cray Time Sharing System (CTSS) de LLL . . CTSS fue escrito en una memoria dinámica Fortran, primero llamado LRLTRAN, que se ejecutaba en CDC 7600s , renombrado CVC (pronunciado "Civic") cuando se agregó la vectorización para el Cray-1. Cray Research intentó respaldar estos sitios en consecuencia. Estas opciones de software influyeron en las minisupercomputadoras posteriores , también conocidas como " crayettes ".

NCAR tiene su propio sistema operativo (NCAROS).

La Agencia de Seguridad Nacional desarrolló su propio sistema operativo (Folklore) y lenguaje (IMP con puertos de Cray Pascal y C y Fortran 90 más tarde)

Las bibliotecas comenzaron con las propias ofertas de Cray Research y Netlib .

Existían otros sistemas operativos, pero la mayoría de los lenguajes tendían a estar basados en Fortran o Fortran. Bell Laboratories , como prueba tanto del concepto de portabilidad como del diseño del circuito, trasladó el primer compilador de C a su Cray-1 (no vectorización). Este acto más tarde le daría la IRC una ventaja inicial de seis meses en el Cray-2 puerto de Unix a ETA Sistemas 'en detrimento, y Lucasfilm ' primera película de prueba generados por computadora s, Las aventuras de André y Wally B. .

El software de aplicación generalmente tiende a ser clasificado ( por ejemplo , código nuclear, código criptoanalítico) o patentado ( por ejemplo , modelado de yacimientos de petróleo). Esto se debió a que se compartía poco software entre los clientes y los clientes universitarios. Las pocas excepciones fueron los programas climatológicos y meteorológicos hasta que la NSF respondió al proyecto japonés de sistemas informáticos de quinta generación y creó sus centros de supercomputadoras. Incluso entonces, se compartió poco código.

En parte porque Cray estaba interesado en la publicidad, apoyaron el desarrollo de Cray Blitz, que ganó el cuarto (1983) y el quinto (1986) Campeonato Mundial de Ajedrez Informático , así como el Campeonato Norteamericano de Ajedrez Informático de 1983 y 1984 . El programa, Chess , que dominó en la década de 1970, se ejecutaba en supercomputadoras de Control Data Corporation.

Museos

Los Cray-1 están en exhibición en las siguientes ubicaciones:

- Museo de Ciencias Bradbury en Los Alamos, Nuevo México

- Museo de Industria y Tecnología de Chippewa Falls en Chippewa Falls, Wisconsin

- Las oficinas de Cray Inc. en Cray Plaza en St. Paul, Minnesota

- Museo de Historia de la Computación en Mountain View, California

- Museo de la Computación de América, Roswell, Georgia, EE. UU.

- Museo de la Computación DigiBarn

- Deutsches Museum en Múnich

- ETH Zurich - Eidgenössische Technische Hochschule Zürich , Suiza

- Living Computers: Museum + Labs en Seattle, Washington

- Centro Nacional de Investigación Atmosférica en Boulder, Colorado

- Museo Nacional del Aire y el Espacio en Washington, DC

- Musée Bolo en Lausana , Suiza

- El Museo Nacional de Computación en Bletchley Park

- Museo de Ciencias de Londres

- Museo Nacional Sueco de Ciencia y Tecnología en Estocolmo, Suecia

Otras imágenes del Cray-1

Cray-1 en el Museo de Historia de la Computación

Cray-1 en el Museo de Historia de la Computación

Cray-1 en Deutsches Museum

The Cray-1 en el Museo de Ciencias de Londres

Referencias

enlaces externos

- CRAY-1 Computer System Hardware Reference Manual , Publicación No. 2240004 Rev.C 11/77 (primeros tres capítulos) - De DigiBarn / Ed Thelen

- Manual de referencia del hardware del sistema informático CRAY-1 , publicación n.o 2240004 Rev.C 11/77 (completo, escaneado, PDF)

- Colección de manuales y documentación de Cray en línea @ Bitsavers

- Revista Cray Channels @ The Center for Computing History

- Manuales y documentación de Cray @ The Center for Computing History

- Publicaciones de Cray Users Group @ The Center for Computing History

- Galería de supercomputadoras NCAR

- Definición de Verilog de la lógica de CPU Cray-1A