VIA Nano - VIA Nano

| |

| Información general | |

|---|---|

| Comercializado por | VIA Technologies |

| Diseñada por | Tecnología Centaur |

| Fabricante (s) común (es) | |

| Rendimiento | |

| Velocidades FSB | 533 MHz a 1066 MHz |

| Cache | |

| Caché L1 | Instrucción de 64 KiB + datos de 64 KiB por núcleo |

| Caché L2 | 1 MiB por núcleo |

| Arquitectura y clasificación | |

| Min. tamaño de la característica | 40 nm hasta 65 nm |

| Microarquitectura | VIA Isaías |

| Conjunto de instrucciones | x86-64 |

| Especificaciones físicas | |

| Núcleos | |

| Paquete (s) | |

| Productos, modelos, variantes | |

| Nombre (s) principal | |

| Historia | |

| Predecesor | VIA C7 |

El VIA Nano (anteriormente llamado VIA Isaiah ) es una CPU de 64 bits para computadoras personales . El VIA Nano fue liberado por VIA Technologies en 2008 después de cinco años de desarrollo de su división de CPU, Centaur Tecnología . Esta nueva arquitectura Isaiah de 64 bits se diseñó desde cero, se dio a conocer el 24 de enero de 2008 y se lanzó el 29 de mayo, incluidas las variantes de bajo voltaje y la marca Nano. El procesador admite una serie de extensiones x86 específicas de VIA diseñadas para aumentar la eficiencia en dispositivos de bajo consumo.

Historia

A diferencia de Intel y AMD , VIA usa dos nombres de código de desarrollo distintos para cada uno de sus núcleos de CPU. En este caso, el nombre en clave 'CN' fue utilizado en los Estados Unidos por Centaur Technology. Los nombres bíblicos se utilizan como códigos por VIA en Taiwán , e Isaiah fue la elección para este procesador y arquitectura en particular. Se espera que el VIA Isaiah sea dos veces más rápido en rendimiento de números enteros y cuatro veces más rápido en rendimiento de punto flotante que el VIA Esther de la generación anterior a una velocidad de reloj equivalente . También se espera que el consumo de energía esté a la par con las CPU VIA de la generación anterior, con una potencia de diseño térmico que varía de 5 W a 25 W. Al ser un diseño completamente nuevo, la arquitectura Isaiah se construyó con soporte para características como la instrucción x86-64 set y virtualización x86 que no estaban disponibles en sus predecesores, la línea VIA C7 , mientras conservaban sus extensiones de cifrado. Varias pruebas independientes demostraron que el VIA Nano funciona mejor que el Intel Atom de un solo núcleo en una variedad de cargas de trabajo. En una prueba de Ars Technica de 2008 , un VIA Nano obtuvo un rendimiento significativo en el subsistema de memoria después de que su CPUID cambió a Intel, lo que sugiere la posibilidad de que el software de referencia solo verifique el CPUID en lugar de las características reales admitidas por la CPU para elegir una ruta de código. El software de referencia utilizado se había lanzado antes del lanzamiento de VIA Nano.

El 3 de noviembre de 2009, VIA lanzó la serie Nano 3000. VIA afirma que estos modelos pueden ofrecer un aumento del rendimiento del 20% y un 20% más de eficiencia energética que las series Nano 1000 y 2000. Los puntos de referencia ejecutados por VIA afirman que un Nano de la serie 3000 a 1.6 GHz puede superar al antiguo Intel Atom N270 en aproximadamente un 40-54%. La serie 3000 agrega las extensiones del conjunto de instrucciones SSE4 SIMD , que se introdujeron por primera vez con revisiones de 45 nm de la arquitectura Intel Core 2 .

El 11 de noviembre de 2011, VIA lanzó el procesador VIA Nano X2 Dual-Core con su primera placa base pico-itx de doble núcleo. El VIA Nano X2 se basa en un proceso de 40 nm y es compatible con las extensiones del conjunto de instrucciones SSE4 SIMD , críticas para las aplicaciones modernas que dependen del punto flotante. Via afirma un rendimiento un 30% más alto en comparación con el Atom de Intel con un reloj un 50% más alto.

Los procesadores de empresas conjuntas Zhaoxin , lanzados a partir de 2014, se basan en la serie VIA Nano.

Características

- conjunto de instrucciones x86-64

- Velocidad de reloj de 1 GHz a 2 GHz

- Velocidad de bus de 533 MHz u 800 MHz (1066 MHz para Nano x2)

- 64 KB de datos e instrucciones de 64 KB de caché L1 y 1 MB de caché L2 por núcleo.

- Proceso de fabricación de 65 nm (40 nm para Nano x2)

- Ejecución de instrucción fuera de orden superescalar

- Soporte para el conjunto de instrucciones MMX, SSE, SSE2, SSE3, SSSE3 y SSE4

- Soporte para virtualización x86 con implementación compatible con Intel (deshabilitado antes del paso 3)

- Soporte para memoria ECC

- Pin-compatible con VIA C7 y VIA Eden

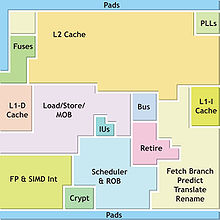

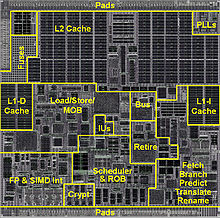

Descripción general de la arquitectura

- Diseño fuera de servicio y superescalar : proporciona un rendimiento mucho mejor que su predecesor, el procesador VIA C7, que estaba en orden. Esto pone la arquitectura Isaiah en línea con las ofertas del mismo año de AMD e Intel.

- Fusión de instrucciones : permite al procesador combinar algunas instrucciones como una única instrucción, lo que reduce los requisitos de energía y brinda un mayor rendimiento (el Atom usa una estrategia similar para procesar instrucciones x86 de una manera más 'completa', en lugar de dividirlas en micro -ops).

- Predicción de rama mejorada : utiliza ocho predictores en dos etapas de canalización.

- Diseño de caché de CPU : un diseño de caché exclusivo significa que el contenido de la caché L1 no se duplica en la caché L2, lo que proporciona una caché total más grande.

-

Captación previa de datos : Incorporación de nuevos mecanismos para la captación previa de datos, incluida la carga de una caché especial de 64 líneas antes de cargar la caché L2 y una carga directa en la caché L1.

- Obtiene 4 instrucciones x86 por ciclo en lugar de las 3-5 de Intel

- Emite 3 microoperaciones / reloj a las unidades de ejecución

- Acceso a la memoria : fusión de almacenes más pequeños en datos de carga más grandes.

-

Unidades de ejecución : se encuentran disponibles siete unidades de ejecución, lo que permite que se ejecuten hasta siete microoperaciones por reloj.

- 2 unidades enteras (ALU1 y ALU2)

- ALU1 tiene funciones completas, mientras que ALU2 carece de algunas instrucciones de bajo uso y, por lo tanto, es más adecuado para tareas como el cálculo de direcciones.

- 2 unidades de almacenamiento, una para el almacenamiento de direcciones y otra para el almacenamiento de datos según VIA .

- 1 unidad de carga

- 2 unidades de medios (MEDIA-A y MEDIA-B) con una ruta de datos de 128 bits de ancho , que admiten 4 operaciones de precisión simple o 2 de precisión doble. El cálculo de medios se refiere al uso de las 2 unidades de medios.

- Ejecuta MEDIA-A "add" instrucciones (latencia 2-reloj de punto flotante de precisión simple y doble precisión ), número entero SIMD, cifrado, división y raíz cuadrada.

- MEDIA-B ejecuta instrucciones de "multiplicación" de punto flotante (latencia de 2 relojes para precisión simple, latencia de 3 relojes para precisión doble).

- Debido al paralelismo introducido con las 2 unidades de medios, el cálculo de medios puede proporcionar cuatro instrucciones de "sumar" y cuatro de "multiplicar" por reloj.

- Una nueva implementación de adición de FP con la latencia de reloj más baja para un procesador x86 hasta ahora.

- Casi todas las instrucciones SIMD enteras se ejecutan en un reloj.

- Implementa conjuntos de instrucciones multimedia MMX , SSE , SSE2 , SSE3 , SSSE3

- Implementa el conjunto de instrucciones multimedia SSE4.1 (serie VIA Nano 3000)

- Implementa el conjunto de instrucciones multimedia SSE4.1 (serie VIA Nano x2)

- 2 unidades enteras (ALU1 y ALU2)

-

Administración de energía : además de requerir muy poca energía, se incluyen muchas características nuevas.

- Incluye un nuevo estado de energía C6 (los cachés se vacían, el estado interno se guarda y el voltaje del núcleo está apagado).

- Control de estado P adaptativo : transición entre los estados de rendimiento y voltaje sin detener la ejecución.

- Overclocking adaptativo : Overclocking automático si hay baja temperatura en el núcleo del procesador.

- Límite térmico adaptable : ajuste del procesador para mantener una temperatura predefinida por el usuario.

-

Cifrado : incluye el motor VIA PadLock

- Soporte de hardware para cifrado AES , algoritmo hash seguro SHA-1 y SHA-256 y generación de números aleatorios

Alrededor del 31/8/2014 aparecieron rumores sobre una posible actualización de Isaías II.

Ver también

Referencias

enlaces externos

prensa

- "La batalla de los procesadores de bajo consumo: la mejor opción para un Nettop" . 2008-09-27. Archivado desde el original el 25 de octubre de 2013.

- "Partido de rencor de gama baja: Nano vs Atom" . 2008-07-30.

- "Via's Nano L2100 adquiere Intel Atom 230" . 2008-07-30.