Alpha 21064 - Alpha 21064

El Alpha 21064 es un microprocesador desarrollado y fabricado por Digital Equipment Corporation que implementó la arquitectura de conjunto de instrucciones (ISA) Alpha (introducido como Alpha AXP ). Fue presentado como DECchip 21064 antes de que cambiara de nombre en 1994. El 21064 también se conoce por su nombre en clave, EV4 . Fue anunciado en febrero de 1992 con disponibilidad de volumen en septiembre de 1992. El 21064 fue la primera implementación comercial del Alpha ISA y el primer microprocesador de Digital disponible comercialmente. Fue sucedido por un derivado, el Alpha 21064A en octubre de 1993.

Historia

El primer procesador Alpha fue un chip de prueba con nombre en código EV3 . Este chip de prueba se fabricó utilizando el proceso CMOS-3 de 1,0 micrómetros (μm) de Digital . El chip de prueba carecía de una unidad de punto flotante y solo tenía cachés de 1 KB . El chip de prueba se utilizó para confirmar el funcionamiento de las técnicas agresivas de diseño de circuitos . El chip de prueba, junto con los simuladores y emuladores, también se utilizó para mostrar el firmware y los diversos sistemas operativos que la empresa admitía.

El chip de producción, con nombre en código EV4 , se fabricó utilizando el proceso CMOS-4 de 0,75 μm de Digital. Dirk Meyer y Edward McLellan fueron los microarquitectos. Ed diseñó la lógica del problema mientras que Dirk diseñó los otros bloques principales. Jim Montanaro dirigió la implementación del circuito. El EV3 se utilizó en la Unidad de demostración Alpha (ADU), un sistema multiprocesador utilizado por Digital para desarrollar software para la plataforma Alpha antes de la disponibilidad de las piezas de EV4.

El 21064 fue presentado en la 39ª Conferencia Internacional de Circuitos de Estado Sólido (ISSCC) a mediados de febrero de 1992. Se anunció el 25 de febrero de 1992, con una muestra de 150 MHz introducida el mismo día. Tenía un precio de $ 3.375 en cantidades de 100, $ 1.650 en cantidades entre 100 y 1.000 y $ 1.560 en cantidades superiores a 1.000. Los envíos por volumen comenzaron en septiembre de 1992.

A principios de febrero de 1993, el precio de la versión de 150 MHz se redujo a $ 1,096 de $ 1,559 en cantidades superiores a 1,000.

El 25 de febrero de 1993, se introdujo un 200 MHz, con kits de muestra disponibles, a un precio de $ 3.495. En volumen, tenía un precio de $ 1,231 por unidad en cantidades superiores a 10,000. Los pedidos por volumen se aceptaron en junio de 1993 y los envíos en agosto de 1993. En respuesta, se redujo el precio de la versión de 150 MHz. El kit de muestra se redujo a $ 1,690 de $ 3,375, efectivo en abril de 1993; y en volumen, se redujo a $ 853 de $ 1.355 por unidad en cantidades superiores a 10.000, a partir de julio de 1993.

Con la introducción de Alpha 21066 y Alpha 21068 el 10 de septiembre de 1993, Digital ajustó el posicionamiento de los 21064 existentes e introdujo una versión de 166 MHz con un precio de $ 499 por unidad en cantidades de 5,000. El precio de la versión de 150 MHz se redujo a $ 455 por unidad en cantidades de 5,000.

El 6 de junio de 1994, el precio de la versión de 200 MHz se redujo en un 31% a $ 544 para posicionarlo frente al Pentium de 60 MHz; y la versión de 166 MHz en un 19% a 404 dólares por unidad en cantidades de 5.000, a partir del 3 de julio de 1994.

El Alpha 21064 fue fabricado en Digital de Hudson, Massachusetts y Escocia South Queensferry, instalaciones .

Usuarios

El 21064 se utilizó principalmente en computadoras de alta gama, como estaciones de trabajo y servidores . Usuarios incluidos:

- Aspen Systems en sus estaciones de trabajo Alpine

- Carrera Computers en sus estaciones de trabajo Hercules 150, Hercules 200 y Pantera II

- Cray Research , que utilizó el 21064 de 150 MHz en sus supercomputadoras Cray T3D

- Digital, en sus DECpc AXP 150 estaciones de trabajo de nivel básico, 2000 AXP de DEC servidores de nivel de entrada, diciembre 3000 AXP estaciones de trabajo y servidores de nivel de entrada, DEC 4000 AXP servidores de gama media y diciembre 7000/10000 AXP servidores de gama alta

- Encore Computer , en su computadora Infinity R / T de alta gama en tiempo real

Actuación

El 21064 fue el microprocesador de mayor rendimiento desde que se introdujo hasta 1993, después de que International Business Machines (IBM) introdujera el POWER2 de varios chips . Posteriormente se convirtió en el microprocesador de chip único de mayor rendimiento, posición que ocupó hasta que se introdujo el 21064A de 275 MHz en octubre de 1993.

Descripción

El Alpha 21064 es un microprocesador superescalar de doble emisión superpipelinado que ejecuta instrucciones en orden . Es capaz de emitir hasta dos instrucciones en cada ciclo de reloj a cuatro unidades funcionales: una unidad entera , una unidad de punto flotante (FPU), una unidad de dirección y una unidad de rama. La canalización de enteros tiene siete etapas y la canalización de punto flotante diez etapas. Las primeras cuatro etapas de ambas tuberías son idénticas y las implementa I-Box.

Caja I

La I-box es la unidad de control ; busca, decodifica y emite instrucciones y controla la canalización. Durante la etapa uno, se obtienen dos instrucciones del I-cache. La predicción de rama se realiza mediante lógica en el I-box durante la etapa dos. Se utiliza la predicción estática o la predicción dinámica. La predicción estática examinó el bit de signo del campo de desplazamiento de una instrucción de bifurcación , predijo la bifurcación como tomada si el bit de signo indicaba una bifurcación hacia atrás (si el bit de signo contenía 1). La predicción dinámica examinó una entrada en la tabla de historial de ramas de 2048 entradas por 1 bit. Si una entrada contenía 1, la rama se predijo como tomada. Si se utilizó la predicción dinámica, la predicción de rama tiene una precisión de aproximadamente el 80% para la mayoría de los programas. La penalización por predicción errónea de rama es de cuatro ciclos.

Estas instrucciones se decodifican durante la etapa tres. El I-box luego verifica si los recursos requeridos por las dos instrucciones están disponibles durante la etapa cuatro. Si es así, se emiten las instrucciones, siempre que se puedan emparejar. Las instrucciones que podían emparejarse se determinaron por el número de puertos de lectura y escritura en el archivo de registro de enteros. El 21064 podría emitir: un entero opera con una operación de punto flotante, cualquier instrucción de carga / almacenamiento con cualquier instrucción de operación, un entero opera con una rama entera o una operación de punto flotante con una rama de coma flotante. No se permitieron dos combinaciones: una operación de entero y una tienda de punto flotante, y una operación de punto flotante y una tienda de entero. Si una de las dos instrucciones no se puede emitir juntas, las primeras cuatro etapas se detienen hasta que se emita la instrucción restante. Las primeras cuatro etapas también se detienen en caso de que no se pueda emitir ninguna instrucción debido a la falta de disponibilidad de recursos, dependencias o condiciones similares.

La I-caja contiene dos tampones tampón de traducción rápida (TLBs) para traducir direcciones virtuales a direcciones físicas . Estos TLB se denominan búferes de traducción de instrucciones (ITB). La memoria caché de ITB utilizó recientemente entradas de la tabla de páginas para el flujo de instrucciones. Se utiliza una ITB de ocho entradas para las páginas de 8 KB y una ITB de cuatro entradas para las páginas de 4 MB. Ambos ITB son completamente asociativos y utilizan un algoritmo de reemplazo que no se utilizó por última vez.

Ejecución

La ejecución comienza durante la etapa cinco para todas las instrucciones. Los archivos de registro se leen durante la cuarta etapa. Los oleoductos que comienzan en la etapa cinco no se pueden estancar.

Unidad entera

La unidad de enteros es responsable de ejecutar instrucciones de enteros. Consiste en el archivo de registro de enteros (IRF) y el E-box. El IRF contiene treinta y dos registros de 64 bits y tiene cuatro puertos de lectura y dos puertos de escritura que se dividen por igual entre la unidad entera y la unidad de rama. La caja electrónica contiene un sumador , una unidad lógica, un cambiador de barril y un multiplicador . A excepción de las instrucciones de multiplicación, desplazamiento y manipulación de bytes, la mayoría de las instrucciones de números enteros se completan al final de la etapa cinco y, por lo tanto, tienen una latencia de un ciclo. La palanca de cambios de barril está canalizada, pero las instrucciones de manipulación de byte y de desplazamiento no se completan al final de la etapa seis y, por lo tanto, tienen una latencia de dos ciclos. El multiplicador no se canalizó para salvar el área del dado; por tanto, las instrucciones de multiplicación tienen una latencia variable de 19 a 23 ciclos dependiendo de los operandos. En la etapa siete, las instrucciones de números enteros escriben sus resultados en el IRF.

Unidad de dirección

La unidad de dirección, también conocida como "caja A", ejecutaba las instrucciones de carga y almacenamiento. Para permitir que la unidad de dirección y la unidad entera funcionen en paralelo, la unidad de dirección tiene su propio sumador de desplazamiento , que utiliza para calcular direcciones virtuales , en lugar de usar el sumador en la unidad entera. Se utiliza un búfer de búsqueda de traducción (TLB) totalmente asociativo de 32 entradas para traducir direcciones virtuales en direcciones físicas . Este TLB se denomina búfer de traducción de datos (DTB). El 21064 implementó una dirección virtual de 43 bits y una dirección física de 34 bits y, por lo tanto, es capaz de direccionar 8 TB de memoria virtual y 16 GB de memoria física .

Las instrucciones de almacenamiento dan como resultado datos almacenados en un búfer de escritura de 4 entradas por 32 bytes. El búfer de escritura mejoró el rendimiento al reducir el número de escrituras en el bus del sistema al fusionar datos de las tiendas adyacentes y al retrasar temporalmente las tiendas, lo que permite que las cargas se mantengan más rápido ya que el bus del sistema no se utiliza con tanta frecuencia.

Unidad de coma flotante

La unidad de coma flotante consta del archivo de registro de coma flotante (FRF) y el cuadro F. El FRF contiene treinta y dos registros de 64 bits y tiene tres puertos de lectura y dos puertos de escritura. La caja F contenía una tubería de punto flotante y una unidad de división sin tubería que retiraba un bit por ciclo.

El archivo de registro de coma flotante se lee y los datos se formatean en fracción, exponente y signo en la etapa cuatro. Si se ejecutan instrucciones de suma, el sumador calcula la diferencia del exponente y se inicia un detector predictivo de uno o cero inicial que utiliza operandos de entrada para normalizar el resultado. Si ejecuta instrucciones de multiplicar, se genera un multiplicando de 3 X.

En las etapas cinco y seis, se realizan cálculos de alineación o normalización y de bits adhesivos para sumas y restas. Las instrucciones de multiplicación se multiplican en una matriz intercalada bidireccional y canalizada que utiliza un algoritmo de cabina radix-8 . En la etapa ocho, la suma final se realiza en paralelo con el redondeo. Las instrucciones de coma flotante escriben sus resultados en el FRF en la etapa diez.

Las instrucciones ejecutadas en la canalización tienen una latencia de seis ciclos. Las divisiones de precisión simple (32 bits) y de doble precisión (64 bits), que se ejecutan en la unidad de división sin canalización, tienen una latencia de 31 y 61 ciclos, respectivamente.

Cachés

El 21064 tiene dos cachés primarios integrados : un caché de datos de 8 KB (conocido como D-cache) que usa una política de escritura continua y un caché de instrucciones de 8 KB (conocido como I-cache). Ambos cachés se asignan directamente para el acceso de ciclo único y tienen un tamaño de línea de 32 bytes. Las cachés están construidas con celdas de memoria de acceso aleatorio estático (SRAM) de seis transistores que tienen un área de 98 μm 2 . Las cachés tienen 1.024 celdas de ancho por 66 celdas de alto, y las dos filas superiores se utilizan para la redundancia.

Se admitió una caché secundaria externa opcional, conocida como caché B, con capacidades de 128 KB a 16 MB. El caché operó entre un tercio y un dieciseisavo de la frecuencia del reloj interno, o de 12,5 a 66,67 MHz a 200 MHz. El caché B está mapeado directamente y tiene un tamaño de línea de 128 bytes de forma predeterminada que podría configurarse para usar cantidades mayores. Se accede a la caché B a través del bus del sistema.

Interfaz externa

La interfaz externa es un bus de datos de 128 bits que opera entre la mitad y un octavo de la frecuencia del reloj interno, o de 25 a 100 MHz a 200 MHz. El ancho del bus era configurable, los sistemas que usaban el 21064 podían tener una interfaz externa de 64 bits. La interfaz externa también constaba de un bus de direcciones de 34 bits .

Fabricación

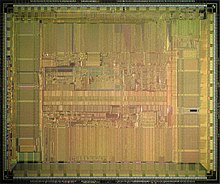

El 21064 contenía 1,68 millones de transistores. El EV4 original fue fabricado por Digital en su proceso CMOS-4, que tiene un tamaño de característica de 0,75 μm y tres niveles de interconexión de aluminio . El EV4 mide 13,9 mm por 16,8 mm, para un área de 233,52 mm 2 . El último EV4S se fabricó en CMOS-4S, una contracción óptica del 10% de CMOS-4 con un tamaño de característica de 0,675 μm. Esta versión medía 12,4 mm por 15,0 mm, para un área de 186 mm 2 .

El 21064 utilizó una fuente de alimentación de 3,3 voltios (V). El EV4 disipó un máximo de 30 W a 200 MHz. El EV4S disipa un máximo de 21,0 W a 150 MHz, 22,5 W a 166 MHz y 27,0 W a 200 MHz.

Paquete

El 21064 está empaquetado en una matriz de rejilla de clavijas de alúmina-cerámica de 431 pines (PGA) que mide 61,72 mm por 61,72 mm. De los 431 pines, 291 eran para señales y 140 eran para alimentación y tierra. El disipador de calor está conectado directamente al paquete, asegurado por tuercas unidas a dos pernos que sobresalen del esparcidor de calor de tungsteno .

Derivados

Alpha 21064A

El Alpha 21064A , presentado como DECchip 21064A , cuyo nombre en código es EV45 , es un desarrollo adicional del Alpha 21064 introducido en octubre de 1993. Operó a frecuencias de reloj de 200, 225, 233, 275 y 300 MHz. El modelo de 225 MHz fue reemplazado por el modelo de 233 MHz el 6 de julio de 1994, que en su introducción tenía un precio de 788 dólares estadounidenses en cantidades de 5.000, un 10% menos que el modelo de 225 MHz que reemplazó. El mismo día, los precios de 275 MHz también se redujeron en un 25% a US $ 1.083 en cantidades de 5.000. El modelo de 300 MHz se anunció y muestreó el 2 de octubre de 1995 y se envió en diciembre de 1995. También había un modelo, el 21064A-275-PC, que estaba restringido a ejecutar Windows NT o sistemas operativos que utilizan la administración de memoria de Windows NT. modelo.

El 21064A sucedió al 21064 original como microprocesador Alpha de gama alta. Posteriormente vio el mayor uso en sistemas de gama alta. Usuarios incluidos:

- Digital en algunos modelos de sus sistemas DEC 3000 AXP, DEC 4000 AXP y DEC 7000/10000 AXP

- Aspen Systems en su estación de trabajo Alpine

- BTG, que utilizó un modelo de 275 MHz en su PC Action AXP275 RISC

- Carrera Computers en su estación de trabajo Cobra AXP 275

- NekoTech, que utilizó un modelo de 275 MHz overclockeado en un 5% a 289 MHz en su estación de trabajo Mach 2-289-T

- Network Appliance (ahora NetApp), que utilizó un modelo de 275 MHz en sus sistemas de almacenamiento

El 21064A tuvo una serie de mejoras de microarquitectura sobre el 21064. Los cachés primarios se mejoraron de dos maneras: la capacidad del I-cache y D-cache se duplicó de 8 KB a 16 KB y se agregó protección de paridad a la etiqueta de caché y matrices de datos de caché. Las divisiones de punto flotante tienen una latencia más baja debido a un divisor mejorado que retira dos bits por ciclo en promedio. La predicción de rama se mejoró con un BHT de 2 bits más grande de 4096 entradas.

El 21064A contiene 2,8 millones de transistores y tiene un tamaño de 14,5 por 10,5 mm, para un área de 152,25 mm 2 . Fue fabricado por Digital en su proceso CMOS de quinta generación, CMOS-5, un proceso de 0,5 μm con cuatro niveles de interconexión de aluminio .

Alpha 21066

El Alpha 21066 , presentado como DECchip 21066 , con el nombre en código LCA4 ( Low Cost Alpha ), es una variante de bajo costo del Alpha 21064. Las muestras se introdujeron el 10 de septiembre de 1993, con envíos por volumen a principios de 1994. En el momento de la introducción , el Alpha 21066 de 166 MHz tenía un precio de 385 dólares estadounidenses en cantidades de 5.000. También existía un modelo de 100 MHz, destinado a sistemas integrados . El muestreo comenzó a fines de 1994, con envíos de volumen en el tercer trimestre de 1995. El Informe de microprocesadores reconoció al Alpha 21066 como el primer microprocesador con un controlador PCI integrado.

El Alpha 21066 fue diseñado para su uso en aplicaciones de bajo costo, específicamente computadoras personales con Windows NT . Digital utilizó varios modelos de Alpha 21066 en sus clientes Multia , placas base de fabricantes de equipos originales (OEM) AXPpci 33 y computadoras de placa única AXPvme . Fuera de Digital, los usuarios incluyeron Aspen Systems en su estación de trabajo Alpine, Carrera Computers en su estación de trabajo Pantera I, NekoTech usó un modelo de 166 MHz en su computadora personal Mach 1-166 y Parsys en sus supercomputadoras TransAlpha TA9000 Series.

Debido a la reducción del proceso, pudo incluir características que eran deseables en sistemas integrados sensibles a los costos . Estas características incluyen un controlador de memoria y caché B en la matriz con soporte ECC , un acelerador de gráficos funcionalmente limitado que admite hasta 8 MB de VRAM para implementar un búfer de tramas , un controlador PCI y un generador de reloj de bucle de bloqueo de fase (PLL) para multiplicar un Señal de reloj externo de 33 MHz a la frecuencia de reloj interna deseada.

El controlador de memoria admitía de 64 KB a 2 MB de caché B y de 2 a 512 MB de memoria. La implementación de ECC fue capaz de detectar errores de 1, 2 y 4 bits y corregir errores de 1 bit. Para reducir el costo, el Alpha 21066 tiene un bus de sistema de 64 bits, lo que reduce la cantidad de pines y, por lo tanto, el tamaño del paquete. El ancho reducido del bus del sistema también redujo el ancho de banda y, por lo tanto, el rendimiento en un 20%, lo que se consideró aceptable.

El 21066 contenía 1,75 millones de transistores y medía 17,0 por 12,3 mm, para un área de 209,1 mm 2 . Fue fabricado en CMOS-4S, un proceso de 0.675 μm con tres niveles de interconexión. El 21066 estaba empaquetado en un CPGA de 287 pines que medía 57,404 por 57,404 mm.

Alpha 21066A

El Alpha 21066A , cuyo nombre en código es LCA45 , es una variante de bajo costo del Alpha 21064A. Se anunció el 14 de noviembre de 1994, con muestras de modelos de 100 y 233 MHz introducidas el mismo día. Ambos modelos se enviaron en marzo de 1995. Cuando se anunciaron, los modelos de 100 y 233 MHz tenían un precio de $ 175 y $ 360, respectivamente, en cantidades de 5,000. Posteriormente se puso a disposición un modelo de 266 MHz.

El 21066A fue adquirido en segundo lugar por Mitsubishi Electric como el M36066A . Fue el primer microprocesador Alpha fabricado por la empresa. Las partes de 100 y 233 MHz se anunciaron en noviembre de 1994. En el momento del anuncio, las muestras de ingeniería se establecieron para diciembre de 1994, las muestras comerciales en julio de 1995 y las cantidades en volumen en septiembre de 1995. La parte de 233 MHz tenía un precio de 490 dólares en cantidades de 1.000 .

Aunque se basó en el 21064A, el 21066A no tenía la memoria caché de instrucciones y datos de 16 KB. Una característica específica del 21066A era la administración de energía: la frecuencia del reloj interno del microprocesador se podía ajustar mediante software.

Digital usó varios modelos de 21066A en sus productos que anteriormente habían usado el 21066. Fuera de Digital, Tadpole Technology usó un modelo de 233 MHz en su portátil ALPHAbook 1 .

El 21066A contenía 1,8 millones de transistores en un troquel de 14,8 por 10,9 mm, para un área de 161,32 mm 2 . Se fabricó en el proceso CMOS de quinta generación de Digital, CMOS-5, un proceso de 0,5 μm con tres niveles de interconexión. Mitsubishi Electric fabricó el M36066A en su propio proceso de metal de tres niveles de 0,5 μm.

Alpha 21068

El Alpha 21068 , presentado como DECchip 21068 , es una versión del 21066 posicionado para sistemas integrados. Era idéntico al 21066 pero tenía una frecuencia de reloj más baja para reducir la disipación de energía y el costo. Las muestras se introdujeron el 10 de septiembre de 1993 con envíos de volumen a principios de 1994. Funcionaba a 66 MHz y tenía una disipación de potencia máxima de 9 W. En el momento de la introducción, el 21068 tenía un precio de 221 dólares estadounidenses cada uno en cantidades de 5.000. El 6 de junio de 1994, Digital anunció que reduciría el precio en un 16% a 186 dólares estadounidenses, a partir del 3 de julio de 1994.

El Alpha 21068 fue utilizado por Digital en su placa base AXPpci 33 y en las computadoras de placa única AXPvme 64 y 64LC .

Alpha 21068A

El Alpha 21068A , presentado como DECchip 21068A , es una variante del Alpha 21066A para sistemas integrados. Operaba a una frecuencia de reloj de 100 MHz.

Chipsets

Inicialmente, no había un chipset estándar para 21064 y 21064A. Las computadoras de Digital usaban circuitos integrados específicos de la aplicación (ASIC) personalizados para conectar el microprocesador al sistema. Como esto elevó el costo de desarrollo para terceros que deseaban desarrollar productos basados en Alpha, Digital desarrolló un chipset estándar, el DECchip 21070 ( Apecs ), para fabricantes de equipos originales (OEM).

Había dos modelos del 21070, el DECchip 21071 y el DECchip 21072 . El 21071 fue diseñado para estaciones de trabajo, mientras que el 21072 fue diseñado para estaciones de trabajo de gama alta o servidores monoprocesador de gama baja. Los dos modelos diferían en las características del subsistema de memoria: el 21071 tiene un bus de memoria de 64 bits y admite de 8 MB a 2 GB de memoria protegida por paridad, mientras que el 21072 tiene un bus de memoria de 128 bits y admite de 16 MB a 4 GB de ECC - memoria protegida.

El chipset consistía en tres diseños de chips: el B-caché y COMANCHE memoria del controlador , el segmento de datos década, y el controlador PCI EPIC. Los chips DECADE implementaron las rutas de datos en segmentos de 32 bits y, por lo tanto, el 21071 tiene dos de estos chips, mientras que el 21072 tiene cuatro. El chip EPIC tiene una ruta de 32 bits a los chips DECADE.

El 21070 se introdujo el 10 de enero de 1994, con muestras disponibles. Los envíos por volumen comenzaron a mediados de 1994. En cantidades de 5,000, el 21071 tenía un precio de $ 90 y el 21072 a $ 120.

Los usuarios de 21070 incluyeron Carrera Computers para sus estaciones de trabajo Pantera y Digital en algunos modelos de sus AlphaStations y AlphaServers monoprocesador .

Notas

Referencias

- Manual de referencia del hardware de los microprocesadores Alpha 21064 y 21064A , junio de 1996. Número de pedido: EC-Q92UC-TE. Corporación de equipos digitales.

- Apiki, Steve; Grehan, Rick (marzo de 1995). "Estaciones de trabajo NT más rápidas" . Byte .

- Bhandarkar, Dileep. "Implementaciones Alfa" , Boletín del Comité Técnico de Arquitectura de Computadoras de IEEE Computer Society , diciembre de 1995.

- Computergram (25 de febrero de 1992). "DEC revela más sobre Alpha, desafía la arquitectura de precisión RISC de Hewlett-Packard" . Revisión de negocios informáticos .

- Computergram (26 de febrero de 1992). "DEC describe su Alpha RISC, Kubota revela sus planes" . Revisión de negocios informáticos .

- Computergram (7 de junio de 1994). "DEC recorta los precios de los chips Alpha AXP hasta en un 31%" . Revisión de negocios informáticos .

- Computergram (13 de septiembre de 1993). "DEC agrega Alphas para Computadoras Personales, Control" . Revisión de negocios informáticos .

- Computergram (11 de enero de 1994). "Los premios anuales de chips del informe de microprocesadores declaran a Motorola 88110 la parte con menos probabilidades de ..." . Revisión de negocios informáticos .

- Computergram (11 de noviembre de 1994). "Mitsubishi Electric está listo para probar su primer Alpha por fin" . Revisión de negocios informáticos .

- Computergram (25 de noviembre de 1994). "El primer Alpha de Mitsubishi ofrece la misma funcionalidad que el 21066A de DEC". Revisión de negocios informáticos .

- Digital Equipment Corporation (10 de enero de 1994). "Digital presenta conjuntos de chips de lógica de sistema basados en PCI para microprocesadores Alpha AXP 21064 y anuncia el primer chip de puente PCI a PCI de la industria". Presione soltar.

- Dobberpuhl, Daniel W., Witek, Richard T. et al. "Un microprocesador CMOS de dos problemas de 200 MHz y 64 bits", Digital Technical Journal , Volumen 4, Número 4, Número especial 1992, págs. 35–50.

- Gwennap, Linley (12 de septiembre de 1994). "Digital lidera el paquete con 21164", informe del microprocesador , volumen 8, número 12.

- Krause, Reinhardt (13 de septiembre de 1993). "DEC presenta dos Alpha en PCI, unidad integrada". Noticias electrónicas .

- Krause, Reinhardt (18 de octubre de 1993). "DEC prepara Alphas de 225/275 MHz". Noticias electrónicas .

- Krause, Reinhardt (21 de noviembre de 1994). "Los socios Alfa ruedan 233MHz 21066A". Noticias electrónicas .

- McKinney, Dina L. et al. "DECchip 21066 de Digital: el primer chip Alpha AXP enfocado en costos". Revista técnica digital , volumen 6, número 1, invierno de 1994, págs. 66–77.

- McLellan, Edward (junio de 1993). "La arquitectura Alpha AXP y el procesador 21064". IEEE Micro . págs. 36–47.

- Ryan, Bob; Thompson, Tom (enero de 1994). "RISC crece" . Byte .

Otras lecturas

- "DEC entra en el negocio de los microprocesadores con Alpha". (4 de marzo de 1992). Informe del microprocesador , volumen 6, número 3.

- "Premiers de Arquitectura Alpha de DEC". (4 de marzo de 1992). Informe del microprocesador , volumen 6, número 3.

- "Amplia familia de procesadores Alpha de Digital Plans" (18 de noviembre de 1992). Informe del microprocesador , volumen 6, número 3.

- "Digital revela conjuntos de chips PCI para Alpha". (12 de julio de 1993). Informe del microprocesador , volumen 7, número 9.

- "Alpha golpea la gama baja con 21066 de Digital". (13 de septiembre de 1993). Informe del microprocesador , volumen 7, número 12.

- Bhandarkar, Dileep P. (1995). Arquitectura e implementaciones Alpha . Prensa digital.

- Fox, Thomas F. (1994). "El diseño de microprocesadores de alto rendimiento en Digital". Actas de la 31ª Conferencia Anual de Automatización de Diseño ACM-IEEE . págs. 586–591.

- Gronowski, Paul E. et al. (Mayo de 1998). "Diseño de microprocesador de alto rendimiento". IEEE Journal of Solid-State Circuits 33 (5): págs. 676–686.