Sistema de conmutación electrónica número uno - Number One Electronic Switching System

El Sistema de Conmutación Electrónica Número Uno ( 1ESS ) fue la primera centralita telefónica o sistema de conmutación electrónica con control de programa almacenado (SPC) a gran escala en el Sistema Bell . Fue fabricado por Western Electric y puesto en servicio por primera vez en Succasunna , Nueva Jersey , en mayo de 1965. El tejido de conmutación estaba compuesto por una matriz de relés de lengüeta controlada por relés de resorte de alambre que a su vez estaban controlados por una unidad central de procesamiento (CPU).

El 1AESS conmutador de la oficina central era un conector compatible , mayor capacidad de actualización de 1ESS con un procesador más rápido 1A que incorpora el conjunto de instrucciones existentes para la programación de compatibilidad, y se utiliza más pequeños remreed interruptores, un menor número de relés y las funciones de almacenamiento en disco . Estuvo en servicio desde 1976 hasta 2017.

Cambio de tejido

El plan de estructura de conmutación de voz era similar al del conmutador 5XB anterior al ser bidireccional y al utilizar el principio de devolución de llamada. Sin embargo, los conmutadores matriciales de acceso completo más grandes (las redes de línea 12A tenían acceso parcial) en el sistema eran 8x8 en lugar de 10x10 o 20x16. Por lo tanto, requerían ocho etapas en lugar de cuatro para lograr grupos de conexiones lo suficientemente grandes en una oficina grande. Como los puntos de cruce son más caros en el nuevo sistema pero los conmutadores son más baratos, el costo del sistema se minimizó con menos puntos de cruce organizados en más conmutadores. La estructura se dividió en redes de línea y redes troncales de cuatro etapas, y se dobló parcialmente para permitir la conexión de línea a línea o troncal a troncal sin exceder las ocho etapas de conmutación.

La implementación tradicional de un conmutador de expansión mínima sin bloqueo capaz de conectar clientes de entrada a clientes de salida simultáneamente, con las conexiones iniciadas en cualquier orden, la matriz de conexión escalada . Siendo esto poco práctico, la teoría estadística se utiliza para diseñar hardware que pueda conectar la mayoría de las llamadas y bloquear otras cuando el tráfico excede la capacidad de diseño. Estos interruptores de bloqueo son los más comunes en las centrales telefónicas modernas. Por lo general, se implementan como tejidos de conmutación más pequeños en cascada. En muchos casos, se utiliza un aleatorizador para seleccionar el inicio de una ruta a través de la estructura de varias etapas, de modo que se puedan obtener las propiedades estadísticas predichas por la teoría. Además, si el sistema de control puede reorganizar el enrutamiento de las conexiones existentes cuando llega una nueva conexión, una matriz sin bloqueo completa requiere menos puntos de conmutación.

Redes de línea y troncales

Cada red de línea (LN) o red troncal (TN) de cuatro etapas se dividió en tramas de conmutador Junctor (JSF) y tramas de conmutador de línea (LSF) en el caso de una red de línea, o tramas de conmutador troncal (TSF) en el caso de una red troncal. Los enlaces se designaron A, B, C y J para Junctor. A Los enlaces eran internos de LSF o TSF; Los enlaces B conectaban LSF o TSF a JSF, C eran internos a JSF y los enlaces J o Junctors estaban conectados a otra red en el intercambio.

Todos los JSF tenían una relación de concentración unitaria, es decir, el número de enlaces B dentro de la red era igual al número de conexiones a otras redes. La mayoría de los LSF tenían una relación de concentración de línea (LCR) de 4: 1; es decir, las líneas eran cuatro veces más numerosas que los enlaces B. En algunas áreas urbanas se utilizaron LSF 2: 1. Los enlaces B a menudo se multiplicaron para hacer un LCR más alto, como 3: 1 o (especialmente en 1ESS suburbano) 5: 1. Las redes de línea siempre tuvieron 1024 conexiones, dispuestas en 16 cuadrículas, cada una de las cuales cambiaba 64 conexiones a 64 enlaces B. Se agruparon cuatro cuadrículas con fines de control en cada uno de los cuatro LJF.

TSF tenía una concentración unitaria, pero un TN podría tener más TSF que JSF. Por lo tanto, sus enlaces B generalmente se multiplicaron para obtener una relación de concentración de troncales (TCR) de 1,25: 1 o 1,5: 1, siendo esta última especialmente común en oficinas 1A. Los TSF y JSF eran idénticos excepto por su posición en el tejido y la presencia de un noveno nivel de acceso de prueba o nivel sin prueba en JSF. Cada JSF o TSF se dividió en 4 cuadrículas de dos etapas.

Los primeros TN tenían cuatro JSF, para un total de 16 cuadrículas, 1024 enlaces J y el mismo número de enlaces B, con cuatro enlaces B desde cada cuadrícula de Trunk Junctor a cada cuadrícula de Trunk Switch. A partir de mediados de la década de 1970, las oficinas más grandes tenían sus enlaces B conectados de manera diferente, con solo dos enlaces B desde cada cuadrícula de conexiones troncales a cada cuadrícula de interruptores troncales. Esto permitió una TN más grande, con 8 JSF que contenían 32 cuadrículas, conectando 2048 conexiones y 2048 enlaces B. Por lo tanto, los grupos de unión podrían ser más grandes y más eficientes. Estos TN tenían ocho TSF, lo que le daba al TN una relación de concentración de tronco unitaria.

Dentro de cada LN o TN, los enlaces A, B, C y J se contaron desde la terminación exterior hasta la interior. Es decir, para una troncal, el interruptor de la etapa 0 de la troncal podría conectar cada troncal a cualquiera de los ocho enlaces A, que a su vez se conectaron a los interruptores de la etapa 1 para conectarlos a los enlaces B. Las redes troncales Junctor también tenían conmutadores de Etapa 0 y Etapa 1, la primera para conectar enlaces B a enlaces C, y la última para conectar enlaces C a J, también llamados Junctors. Los empalmes se reunieron en cables, 16 pares trenzados por cable constituyendo un subgrupo de empalmes, que se extendían hasta el marco de agrupamiento de empalmes, donde se conectaban a los cables de otras redes. Cada red tenía 64 o 128 subgrupos y estaba conectada entre sí mediante uno o (normalmente) varios subgrupos.

La estructura de conmutación 1ESS Ferreed original se empaquetó como interruptores separados de 8x8 u otros tamaños, unidos al resto de la estructura de voz y los circuitos de control mediante conexiones de envoltura de cables . La ruta de transmisión / recepción de la señal de voz analógica es a través de una serie de interruptores de lengüeta con enclavamiento magnético (muy similar a los relés de enclavamiento ).

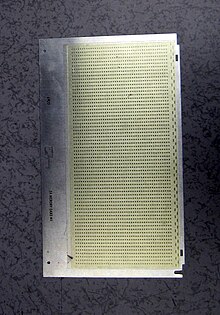

Los puntos de cruce de Remreed, mucho más pequeños, introducidos aproximadamente al mismo tiempo que 1AESS, se empaquetaron como cajas de cuadrícula de cuatro tipos principales. Las rejillas Junctor tipo 10A y las rejillas troncales 11A eran una caja de aproximadamente 16 x 16 x 5 pulgadas (40 x 40 x 12 cm) con dieciséis interruptores de 8 x 8 en el interior. Las rejillas de línea tipo 12A con LCR 2: 1 tenían solo aproximadamente 5 pulgadas (12 cm) de ancho, con ocho interruptores de línea 4x4 Stage 0 con ferrods y contactos de corte para 32 líneas, conectados internamente a cuatro interruptores 4x8 Stage 1 que se conectan a enlaces B. Las rejillas de línea Tipo 14A con LCR 4: 1 tenían aproximadamente 16x12x5 pulgadas (40x30x12 cm) con 64 líneas, 32 enlaces A y 16 enlaces B. Las cajas se conectaron al resto de la estructura y los circuitos de control mediante conectores deslizantes. Por lo tanto, el trabajador tuvo que manejar un equipo mucho más grande y pesado, pero no tuvo que desenvolver y volver a envolver docenas de cables.

Error de tejido

Los dos controladores en cada Junctor Frame tenían acceso sin prueba a sus Junctors a través de su interruptor F, un noveno nivel en los interruptores de la Etapa 1 que se podían abrir o cerrar independientemente de los puntos de cruce en la red. Al configurar cada llamada a través de la estructura, pero antes de conectar la estructura a la línea y / o troncal, el controlador podría conectar un punto de escaneo de prueba a los cables de conversación para detectar potenciales. La corriente que fluye a través del punto de escaneo se informaría al software de mantenimiento, lo que da como resultado un mensaje de teleimpresora "False Cross and Ground" (FCG) que enumera la ruta. Luego, el software de mantenimiento le indicaría al software de finalización de llamadas que vuelva a intentarlo con un conector diferente.

Con una prueba FCG limpia, el software de finalización de llamadas le dijo al relé "A" en el circuito troncal que operara, conectando su transmisión y hardware de prueba a la estructura de conmutación y, por lo tanto, a la línea. Luego, para una llamada saliente, el punto de escaneo de la troncal buscaría la presencia de una línea descolgada. Si no se detectaba el corto, el software ordenaría la impresión de un "Fallo de supervisión" (SUPF) y volvería a intentarlo con un conector diferente. Se realizó una verificación de supervisión similar cuando se respondió a una llamada entrante. Cualquiera de estas pruebas podría alertar sobre la presencia de un punto de cruce incorrecto.

El personal podría estudiar una gran cantidad de impresiones para encontrar qué enlaces y puntos de cruce (de, en algunas oficinas, un millón de puntos de cruce) estaban causando que las llamadas fallaran en los primeros intentos. A finales de la década de 1970, los canales de teleimpresora se reunieron en Switching Control Centers (SCC), más tarde Switching Control Center System , cada uno con una docena o más de intercambios 1ESS y utilizando sus propias computadoras para analizar estos y otros tipos de informes de fallas. Generaron un histograma (en realidad, un diagrama de dispersión ) de partes de la estructura donde las fallas eran particularmente numerosas, generalmente apuntando a un punto de cruce defectuoso en particular, incluso si fallaba esporádicamente en lugar de consistentemente. Los trabajadores locales podrían entonces ocupar el interruptor o la red adecuada y reemplazarlo.

Cuando un punto de cruce de acceso de prueba se atascaba cerrado, causaba fallas FCG esporádicas en todas las redes que fueron probadas por ese controlador. Dado que los enlaces J estaban conectados externamente, el personal de la sala de conmutación descubrió que tales fallas se podían encontrar ocupando ambas redes, conectando a tierra los cables de prueba del controlador y luego probando todos los enlaces 128 J, 256 cables, para una conexión a tierra.

Dadas las restricciones del hardware de la década de 1960, se produjo una falla inevitable. Aunque se detectó, el sistema fue diseñado para conectar a la persona que llama con la persona equivocada en lugar de desconectar, interceptar, etc.

Escanear y distribuir

La computadora recibía entrada de periféricos a través de escáneres magnéticos, compuestos por sensores ferrod, similar en principio a la memoria de núcleo magnético, excepto que la salida estaba controlada por devanados de control análogos a los devanados de un relé . Específicamente, el ferrod era un transformador con cuatro devanados. Dos pequeños devanados atravesaban agujeros en el centro de una varilla de ferrita. Se indujo un pulso en el devanado de interrogación en el devanado de lectura, si la ferrita no estaba saturada magnéticamente . Los devanados de control más grandes, si la corriente fluía a través de ellos, saturaban el material magnético, por lo tanto, desacoplaban el devanado de interrogación del devanado de lectura que devolvería una señal cero. Los devanados de interrogación de 16 ferrods de una fila se conectaron en serie a un controlador, y los devanados de lectura de 64 ferrods de una columna se conectaron a un amplificador sensor. Los circuitos de verificación aseguraron que realmente fluía una corriente de interrogación.

Los escáneres fueron Line Scanners (LSC), Universal Trunk Scanners (USC), Junctor Scanners (JSC) y Master Scanners (MS). Los tres primeros solo escanearon para supervisión , mientras que los Master Scanners hicieron todos los demás trabajos de escaneo. Por ejemplo, un receptor DTMF , montado en un marco de Troncal Misceláneo, tenía ocho puntos de escaneo de demanda, uno para cada frecuencia y dos puntos de escaneo de supervisión, uno para señalar la presencia de una combinación DTMF válida para que el software supiera cuándo mirar el puntos de escaneo de frecuencia, y el otro para supervisar el bucle. El punto de exploración de supervisión también detectó Dial Pulses, con el software contando los pulsos a medida que llegaban. Cada dígito cuando se convirtió en válido se almacenó en una tolva de software para ser entregado al Registro de origen.

Los ferrods se montaban en pares, generalmente con diferentes devanados de control, por lo que uno podía supervisar un lado de un maletero hacia el interruptor y el otro la oficina distante. Los componentes dentro del paquete del maletero, incluidos los diodos, determinaron, por ejemplo, si realizaba una señalización inversa de la batería como un maletero entrante o detectaba una batería inversa desde un maletero distante; es decir, era un tronco saliente.

Los ferrods de línea también se proporcionaron en pares, de los cuales el número par tenía contactos traídos al frente del paquete en orejetas adecuadas para envoltura de alambre para que los devanados pudieran atarse para inicio de bucle o señalización de inicio de tierra . El empaque original de 1ESS tenía todos los ferrods de un LSF juntos y separados de los interruptores de línea, mientras que el 1AESS posterior tenía cada ferrod en la parte delantera de la caja de acero que contenía su interruptor de línea. Los equipos de líneas impares no se podían poner en marcha desde el suelo, ya que sus ferrods eran inaccesibles.

La computadora controlaba los relés de enclavamiento magnético mediante los Distribuidores de señales (SD) empaquetados en los marcos Universal Trunk, Junctor o en varios marcos Trunk, según los cuales estaban numerados como USD, JSD o MSD. Los SD eran originalmente árboles de contactos de relés de resorte de alambre de 30 contactos , cada uno impulsado por un flip-flop. Cada relé de enclavamiento magnético tenía un contacto de transferencia dedicado a enviar un pulso de regreso a la SD, en cada operación y liberación. El generador de pulsos en la SD detectó este pulso para determinar que la acción había ocurrido, o alertó al software de mantenimiento para que imprimiera un informe FSCAN . En versiones posteriores de 1AESS, las SD eran de estado sólido con varios puntos SD por tarjeta, generalmente en el mismo estante o estante adyacente al paquete de troncales.

Algunos periféricos que necesitaban un tiempo de respuesta más rápido, como los transmisores de pulsos de marcación, se controlaban a través de distribuidores de pulsos centrales, que de otro modo se usaban principalmente para habilitar (alertar) a un controlador de circuito periférico para aceptar órdenes del bus de direcciones de la unidad periférica.

Computadora 1ESS

El procesador central de arquitectura Harvard duplicado o CC (Control Central) para el 1ESS operaba a aproximadamente 200 kHz . Constaba de cinco bahías, cada una de dos metros de altura y con un total de unos cuatro metros de longitud por CC. El empaque estaba en tarjetas de aproximadamente 4 x 10 pulgadas (10 x 25 centímetros) con un conector de borde en la parte posterior. Cableado plano posterior era de algodón cubierto por arrollamiento de hilo cables, no cintas u otros cables. La lógica de la CPU se implementó utilizando lógica discreta de diodo-transistor . Una tarjeta de plástico duro solía contener los componentes necesarios para implementar, por ejemplo, dos puertas o un flip-flop .

Se dedicó mucha lógica a los circuitos de diagnóstico. Se podrían ejecutar diagnósticos de CPU que intentarían identificar las tarjetas defectuosas. En las fallas de una sola tarjeta, el primer intento de reparar las tasas de éxito del 90% o más fue común. Las fallas múltiples de tarjetas no eran infrecuentes y la tasa de éxito de la primera reparación disminuyó rápidamente.

El diseño de la CPU era bastante complejo: utilizaba un entrelazado de tres vías de ejecución de instrucciones (más tarde llamado canalización de instrucciones ) para mejorar el rendimiento. Cada instrucción pasaría por una fase de indexación, una fase de ejecución de instrucción real y una fase de salida. Mientras una instrucción pasaba por la fase de indexación, la instrucción anterior estaba en su fase de ejecución y la instrucción anterior estaba en su fase de salida.

En muchas instrucciones del conjunto de instrucciones , los datos se pueden enmascarar y / o rotar opcionalmente . Existían instrucciones únicas para funciones esotéricas como " buscar el primer bit establecido (el bit más a la derecha que está establecido) en una palabra de datos, opcionalmente restablecer el bit y decirme la posición del bit". Tener esta función como una instrucción atómica (en lugar de implementarla como una subrutina ) aceleró drásticamente el escaneo de solicitudes de servicio o circuitos inactivos. El procesador central se implementó como una máquina de estado jerárquica .

La memoria tenía una longitud de palabra de 44 bits para los almacenes de programas, de los cuales seis bits eran para la corrección de errores de Hamming y uno se utilizaba para una verificación de paridad adicional. Esto dejó 37 bits para la instrucción, de los cuales generalmente se usaron 22 bits para la dirección. Esta fue una palabra de instrucción inusualmente amplia para la época.

Los almacenes de programas también contenían datos permanentes y no se podían escribir en línea. En cambio, las tarjetas de memoria de aluminio, también llamadas planos twistor, tuvieron que ser removidas en grupos de 128 para que sus imanes permanentes pudieran ser escritos fuera de línea por un escritor motorizado, una mejora con respecto al escritor de una sola tarjeta no motorizado usado en el Proyecto Nike . Todos los marcos de memoria, todos los buses y todo el software y los datos eran completamente redundantes, modulares duales . Los CC duales funcionaron en sincronía y la detección de una falta de coincidencia activó un secuenciador automático para cambiar la combinación de CC, buses y módulos de memoria hasta que se alcanzó una configuración que pudiera pasar una verificación de cordura . Los buses eran pares trenzados , un par para cada dirección, datos o bit de control, conectados en el CC y en cada trama de la tienda mediante transformadores de acoplamiento y terminando en resistencias terminales en la última trama.

Los almacenes de llamadas eran la memoria de lectura / escritura del sistema, que contenía los datos de las llamadas en curso y otros datos temporales. Tenían una palabra de 24 bits , de los cuales un bit era para verificación de paridad . Operaron de manera similar a la memoria de núcleo magnético , excepto que la ferrita estaba en hojas con un orificio para cada bit, y la dirección de corriente coincidente y los cables de lectura pasaron a través de ese orificio. Las primeras Call Stores tenían 8 kilovatios , en un marco de aproximadamente un metro de ancho y dos metros de alto.

La memoria de programa separada y la memoria de datos se operaron en antifase, coincidiendo la fase de direccionamiento de Program Store con la fase de obtención de datos de Call Store y viceversa. Esto resultó en una mayor superposición, por lo tanto, una mayor velocidad de ejecución del programa de lo que podría esperarse de la baja frecuencia del reloj.

Los programas se escribieron principalmente en código de máquina. Los errores que anteriormente pasaban desapercibidos se volvieron prominentes cuando 1ESS se llevó a las grandes ciudades con mucho tráfico telefónico y retrasó la adopción total del sistema durante algunos años. Las soluciones temporales incluyeron la red de enlace de servicio (SLN), que hizo aproximadamente el trabajo del enlace de registro entrante y el conmutador de selección de timbre del conmutador 5XB , lo que disminuyó la carga de la CPU y los tiempos de respuesta para las llamadas entrantes, y un procesador de señal (SP) o computadora periférica de una sola bahía, para manejar tareas simples pero que requieren mucho tiempo, como la sincronización y el conteo de los pulsos de marcación. 1AESS eliminó la necesidad de SLN y SP.

La unidad de cinta de media pulgada era solo de escritura y se usaba solo para la contabilidad automática de mensajes . Las actualizaciones del programa se ejecutaron enviando una carga de tarjetas Program Store con el nuevo código escrito en ellas.

El programa Basic Generic incluía "auditorías" constantes para corregir errores en los registros de llamadas y otros datos. Cuando ocurría una falla crítica de hardware en el procesador o en las unidades periféricas, como cuando ambos controladores de un marco de conmutador de línea fallaban y no podían recibir órdenes, la máquina dejaba de conectar llamadas y entraba en una "fase de regeneración de memoria", "fase de reinicialización". ", o" Fase "para abreviar. Las Fases se conocían como Fase 1, 2, 4 o 5. Las fases menores solo borraban los registros de llamadas de las llamadas que estaban en un estado inestable que aún no estaban conectadas y tomaban menos tiempo.

Durante una Fase, el sistema, normalmente rugiendo con el sonido de los relés funcionando y soltándose, se silenciaba ya que ningún relé recibía órdenes. El Teletype Model 35 sonaba e imprimía una serie de P mientras duraba la fase. Para el personal de la oficina central, esto podría ser un momento aterrador, ya que pasaron segundos y luego tal vez minutos mientras sabían que los suscriptores que levantaran sus teléfonos se quedarían en silencio hasta que la fase terminara y el procesador recuperara la "cordura" y reanudara la conexión de llamadas. Las fases más extensas tomaron más tiempo, borrando todos los registros de llamadas, desconectando así todas las llamadas y tratando cualquier línea descolgada como una solicitud de tono de marcación. Si las fases automatizadas no lograban restaurar la cordura del sistema, existían procedimientos manuales para identificar y aislar el hardware o los buses defectuosos.

1AESS

La mayoría de las miles de oficinas 1ESS y 1AESS en los EE. UU. Fueron reemplazadas en la década de 1990 por DMS-100 , 5ESS Switch y otros conmutadores digitales, y desde 2010 también por conmutadores de paquetes . A finales de 2014, quedaban poco más de 20 instalaciones de 1AESS en la red de América del Norte, que estaban ubicadas principalmente en los estados heredados de BellSouth de AT&T y Southwestern Bell de AT&T, especialmente en el área metropolitana de Atlanta GA, el área metropolitana de Saint Louis MO y en el Área metropolitana de Dallas / Fort Worth TX. En 2015, AT&T no renovó un contrato de soporte con Alcatel-Lucent (ahora Nokia ) para los sistemas 1AESS que aún estaban en funcionamiento y notificó a Alcatel-Lucent de su intención de retirarlos del servicio para 2017. Como resultado, Alcatel-Lucent desmanteló el último laboratorio 1AESS en la ubicación de Naperville Bell Labs en 2015, y anunció la interrupción del soporte para 1AESS. En 2017, AT&T completó la eliminación de los sistemas 1AESS restantes al trasladar a los clientes a otros conmutadores de tecnología más nueva, generalmente con conmutadores Genband con trunking TDM únicamente.

El último conmutador 1AESS conocido estaba en Odessa, TX (Odessa Lincoln Federal wirecenter ODSSTXLI). Se desconectó del servicio alrededor del 3 de junio de 2017 y se transfirió a un conmutador de paquetes Genband G5 / G6.